Kai-Uwe Sattler Alfons Kemper Thomas Neumann Jens Teubner *Editors*

# Scalable Data Management for Future Hardware

**Editors**

Kai-Uwe Sattler, Alfons Kemper, Thomas Neumann and Jens Teubner

# Scalable Data Management for Future Hardware

**Editors**

Kai-Uwe Sattler

Databases and Information Systems Group, TU Ilmenau, Ilmenau, Germany

Alfons Kemper Chair of Database Systems, TU München, Garching, Germany

Thomas Neumann Chair of Data Science and Engineering, TU München, Garching, Germany

Jens Teubner Databases and Information Systems Group, TU Dortmund, Dortmund, Germany

ISBN 978-3-031-74096-1 e-ISBN 978-3-031-74097-8 https://doi.org/10.1007/978-3-031-74097-8

This work was founded by the German Research Foundation (DFG) as part of the priority programs "Scalable Data Management for Future Hardware" (SPP 2037).

© The Editor(s) (if applicable) and The Author(s) 2025. This book is an open access publication.

**Open Access** This book is licensed under the terms of the Creative Commons Attribution 4.0 International License

(http://creativecommons.org/licenses/by/4.0/), which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license and indicate if changes were made.

The images or other third party material in this book are included in the book's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the book's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, expressed or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Switzerland AG

The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

#### **Foreword**

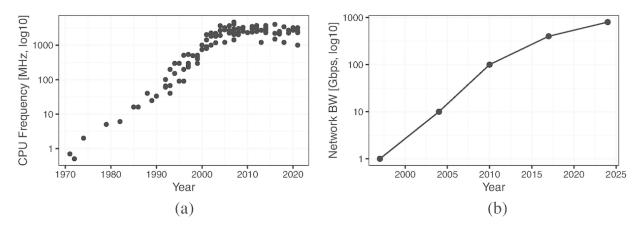

Computer science and the IT industry are currently undergoing significant and fundamental changes at many levels. On the one hand, the business model has evolved from a manufacturing industry (software and hardware) to a service industry based on cloud providers offering hardware and software as a service. This alone has enormous implications for the technology as the economies of scale and the highly shared infrastructure of the cloud create opportunities for optimization and specialization not available before. On the other hand, the relevant applications, use cases, and workloads have become mainly data driven, involving extraordinary amounts of data and very tight performance as well as efficiency requirements. These changes are happening at a time where limitations at the physical and economic level prevent us from producing faster general-purpose processors (CPUs), a drawback that is being addressed through hardware specialization where use-case-specific hardware is developed to be able to meet the requirements of common applications.

The Scalable Data Management for Future Hardware of the DFG priority program has tackled these challenges from the perspective of data processing, a cornerstone of data science and the machine learning revolution we are experiencing. Data management systems, and especially relational databases, are still one of the largest software industries. Neither the cloud nor machine learning has changed that. However, their role and how they are used have changed and are quickly evolving. For instance, on the software side, now all major database machines support vector search and large-scale vectors, something that would have been difficult to imagine just 5 years ago given the characteristics of vector data and the operations performed over it. On the hardware side, there is a growing

amount of examples from both industry and academia of tailoring database engines to new hardware (networking, new memory models, new processors, accelerators, etc.). The researchers in the program have pioneered and led many of these efforts, their work having now become a major reference for anybody exploring the area. The program has also been a great, and much needed, source of talent covering both the data management and the hardware specialization side, creating the basis for future research and education programs.

The chapters in this book provide a glimpse of the highly innovative work done as part of the program, covering topics that encompass from new memory models and new memory technologies to heterogeneous computing, tackling research questions related to high-scale parallelism, consistency, bottlenecks caused by interconnects, reconfigurable computing, modern networking, and nonvolatile memory in the context of various applications (query processing, graph databases, event processing, etc.). The work reported provides a comprehensive coverage of the topics and provides excellent examples of the opportunities new hardware has to offer. It is important to note that the topics explored do so in great detail, not only in terms of describing a design but also exploring the practical implications for data management systems and database engines in terms of how their architecture needs to evolve. It is also interesting that the book covers a very insightful spectrum between ideas that can be applied to existing engines without having to do major changes to radically new designs that open up intriguing opportunities for future systems.

Data management is and remains a key component of the data science revolution, maybe attracting less attention than machine learning and large language models but still acting as a key enabler and a source of ideas to improve the performance and efficiency of what are now the largest data processing engines ever built. But data management systems need to evolve with the times, and that requires to adapt and adopt new hardware. This book summarizes an impressive amount of work done in the priority program in this direction, with many valuable insights that will serve as inspiration for future work and also having trained the first generation of researchers equipped to address the challenges ahead of us.

Gustavo Alonso Zurich June 2024

#### **Preface**

Data management is one of the central tasks in many applications and an indispensable component in modern IT stacks. The spectrum of applications ranges from managing structured business data in ERP or ordering systems, over answering queries in decision-support systems, backends on cloud applications, or embedded systems, to managing data and models in AI applications. The requirements have continued to evolve in recent years: While initially the management transactional data with consistency (ACID) guarantees was the main tasks of database systems, modern data management solutions now also support complex analyses on very differently structured data (from tables, graphs, and semi-structured data to texts, images, and videos) through to highly dynamic data streams. Data management systems typically provide abstractions for the application layers above them: data structures and models for representing data, query languages for accessing and processing data, and system abstractions for transparently leveraging storage hierarchies or parallel or distributed architectures. However, the efficient implementation of data management requires leveraging the underlying layers down to the hardware, with the boundaries constantly shifting. While disk-based external storage used to be the bottleneck in the past, main memory accesses or concurrency control in multi-core systems are now performance critical. At the same time, hardware developments in recent years offer a wide range of possibilities for efficient use in data management tasks. Examples are:

Multi-core CPUs: Modern CPUs offer up to 100 cores at the commodity level, and next-generation CPUs are expected to offer several hundred cores. To enable high levels of parallelism, some architectures already provide

- hardware support for the necessary synchronization, such as transactional memory. Leveraging this parallelism for database processing is still an open question.

- Co-processors such as GPUs and FPGAs: Special-purpose computing devices such as GPUs and FPGAs allow for much higher levels of parallelism, significantly accelerating compute-intensive tasks, including database tasks. In addition, heterogeneous hardware designs such as coupled CPU-FPGA and CPU-GPU architectures, as well as fast interconnects between the CPU and coprocessing units, represent a trend toward tighter integration that makes expensive data transfers cheaper or even unnecessary.

- Novel memory and storage technologies like NVRAM and SSD: Modern in-memory database system solutions still rely mostly on block-based media for ensuring persistence of data. In recent years, memory technologies such as non-volatile or persistent memory (PMem) have promised byte-addressable persistence with latencies close to DRAM. Though commercial PMem products are discontinued, emerging technologies such as CXL offer new opportunities for architectures with remote, shared, or disaggregated memory. These memory technologies together with advances in SSD performance require to revisit memory and storage hierarchies in data management systems.

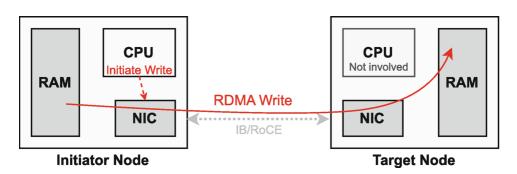

- High-speed networks: Both in scale-up and scale-out scenarios, efficient interconnects play a crucial role.

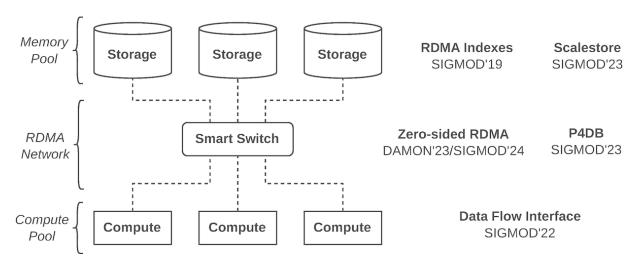

Network technologies like RDMA (Remote DMA), e.g., based on Gbit Ethernet or InfiniBand, provide direct access to memory of remote nodes. Furthermore, smart network interface cards (NIC) can act as accelerators for in-network processing. Utilizing these technologies in database systems requires new concepts.

Based on these observations, we derived the thesis that data management architectures need to undergo a radical shift to meet current and future requirements. Since 2017, we have been tackling this challenge within the framework of the DFG-funded priority program SPP 2037 "Scalable Data Management for Future Hardware." The goal of the priority program was to bring together researchers from the fields of database systems, operating systems, and distributed systems to investigate the possibilities and consequences of modern and future hardware in system architectures for data management.

In two 3-year phases, a total of 12 projects from 22 PIs investigated a wide range of data management architectures in conjunction with current hardware developments. The program was accompanied by two Dagstuhl seminars (Seminar 18251, "Database Architectures for Modern Hardware," 2018, and Seminar 21283, "Data Structures for Modern Memory and Storage Hierarchies," 2021) as well as regular internal workshops. The results of this priority are summarized in this book. In nine chapters, the authors present results primarily from the second phase of the program.

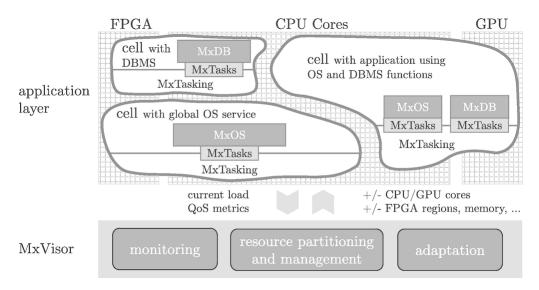

In Chap. 1, "ADAMANT: Hardware-Accelerated Query Processing Made Easy," an approach for the integration of co-processing units such as FPGA and GPUs is presented that supports cross-device parallelization of SQL queries. Furthermore, techniques for FPGA-based query-specific hardware acceleration as well as approximate query processing are introduced.

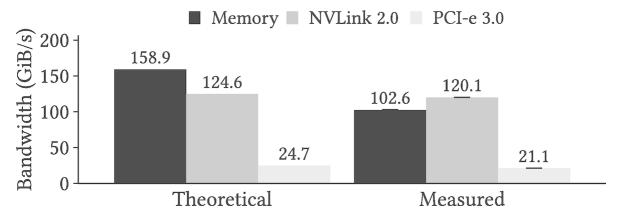

Heterogeneous hardware environments are also addressed in Chap. 2, "Query Processing on Heterogeneous Hardware," by exploring methodologies for executing database queries on any processor without manual adjustments. For this purpose, a compilation of database and stream processing queries into optimized code is discussed considering the use of GPUs, workload

distribution, and data transfer bottlenecks, e.g., by examining NVLink 2.0 technology.

Next, in Chap. 3, "Efficient Event Processing on Modern Hardware," the domain of complex event processing with both continuous queries and analytical ad hoc queries is considered. Multi-core CPUs and GPUs are explored for efficient processing of pattern-matching operators, while modern storage technologies are used for ingestion and ad hoc queries.

In Chap. 4, "Hybrid Transactional/Analytical Graph Processing in Modern Memory Hierarchies," the authors exploit modern memory hierarchies including persistent memory for graph database systems supporting hybrid transactional/analytical (HTAP) workloads. In addition, graph analysis in GPU-based accelerators with dedicated memory is enabled by efficient mechanisms for data transfer and consistency.

Chapter 5, "MxKernel: A Bare-Metal Runtime System for Database Operations on Heterogeneous Many-Core Hardware," presents a runtime environment that provides control flow primitives called MxTasks that can be annotated with application-specific hints. Using such hints, the runtime system provides automatic synchronization, prefetching, and dynamic resource partitioning.

The authors of Chap. 6 "Scaling beyond DRAM without Compromising Performance" present approaches for scaling database systems beyond the main memory capacity of a single server. This includes system approaches for a storage engine and PMem-optimized storage for transactional workloads, a programming model for disaggregated systems, and a just-in-time query compilation framework for ARM processors.

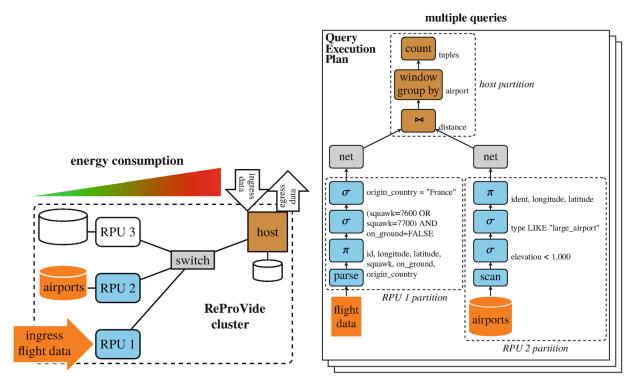

The topic of Chap. 7, "ReProVide: Query Optimization and Near-Data Processing on Reconfigurable SoCs for Big Data Analysis," is near-data processing using FPGA accelerators. Based on a SoC architecture, a reconfigurable

approach for flexible loading and execution of query operators on relational and streaming data is presented.

The work presented in Chap. 8, "Scalable Data Management on Next-Generation Data Center Networks," examines how modern network infrastructure such as RDMA affects the design of disaggregated databases. In addition to RDMA, programmable networks are considered for database processing by presenting in-network OLTP processing and a network-driven data shuffling approach.

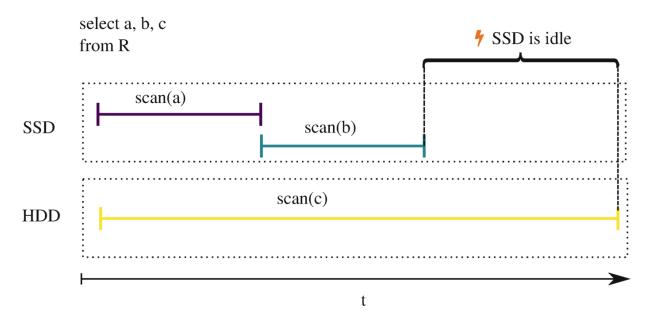

Finally, the authors of Chap. 9, "Managing Very Large Data Sets on Directly-Attached NVMe Arrays," discuss the impact of modern fast storage devices such as NVMe arrays on the architecture and implementation of storage engines for database systems. Based on an evaluation of the performance tradeoffs, they show that the aggregated bandwidth of ten or more NVMe SSDs can approach main memory.

We hope that this book will not only give readers an insight into the results of the program but also provide inspiration for future work beyond the database area. Especially a comprehensive system view as a combination of data management, operating systems, distributed systems, and computer architecture is on the one hand necessary to address the requirements from practice and on the other hand offers great potential for innovative ideas and exciting research questions.

Kai-Uwe Sattler

Alfons Kemper

Thomas Neumann

Jens Teubner

Ilmenau, Germany

Garching, Germany

Garching, Germany

Dortmund, Germany

#### **June 2024**

#### Acknowledgements

The work presented in this book was funded by the German Research Foundation (DFG) in the context of the priority program SPP 2037 "Scalable Data Management for Future Hardware."

We would like to thank the DFG for the funding, without which this research work would not have been possible.

We also thank the members of our advisory board, Goetz Graefe, Peter Boncz, Theo Härder, and Franz Färber, who accompanied us, especially at the beginning of the program.

Finally, we thank all reviewers of the program, the projects, and our research papers for their valuable feedback.

#### **Contents**

## 1 ADAMANT: Hardware-Accelerated Query Processing Made Easy

David Broneske, Vitalii Burtsev, Anna Drewes, Bala Gurumurthy, Thilo Pionteck and Gunter Saake

- 1.1 Introduction

- 1.2 Challenges for ADAMANT's Plug'n'Play Architecture

- 1.2.1 C1: Device-Specific Processing Capabilities

- 1.2.2 C2: Exploitation of Full Processing Power

- 1.2.3 C3: Effective Parallel Execution of Multiple Queries

- 1.3 Approximate Query Processing

- 1.3.1 Approximation Approaches

- 1.3.2 Bag of Little Bootstraps

- 1.3.3 Streaming BLB

- 1.3.4 FPGA-Based Bag of Little Bootstraps

- 1.3.5 Test Setup

- 1.3.6 Evaluation

- 1.3.7 Conclusion

- 1.4 Device-Specific Primitive Graphs

- 1.4.1 Primitives

- 1.4.2 Grouped Aggregation as Device-Specific Primitive

- 1.4.3 Primitive Libraries

- 1.4.4 Primitive Fusion

#### 1.5 FPGA Overlay Template

- 1.5.1 Motivation

- 1.5.2 Investigation of OpenCL-Based HLS

- 1.5.3 FPGA Overlay Template

- **1.5.4 Results**

- **1.6 Cross-Device Query Execution Methods**

- 1.6.1 4-Phase Chunked Execution for Cross-Device Execution

- **1.6.2 Combining Compiled and Interpreted Execution**

- 1.7 Multi-query Processing

- 1.7.1 Motivation

- **1.7.2 Method**

- 1.7.3 Evaluation

- 1.7.4 Conclusion

- 1.8 Conclusion

#### **References**

#### 2 Query Processing on Heterogeneous Hardware

Anastasiia Kozar, Janis von Bleichert, Sebastian Breß, Philipp M. Grulich, Clemens Lutz, Tilmann Rabl, Viktor Rosenfeld, Jonas Traub, Steffen Zeuch and Volker Markl

- 2.1 Introduction

- 2.2 Background

- 2.2.1 Query Compilation

- 2.2.2 Compilers

- 2.2.3 Databases on Heterogeneous Hardware

- 2.3 Query Processing on Heterogeneous CPU/GPU Systems

- 2.3.1 Processor Architectures

- 2.3.2 Conventional CPUs

- 2.3.3 Dedicated GPUs

- 2.3.4 GPU Integration

- 2.3.5 GPU Programming Model

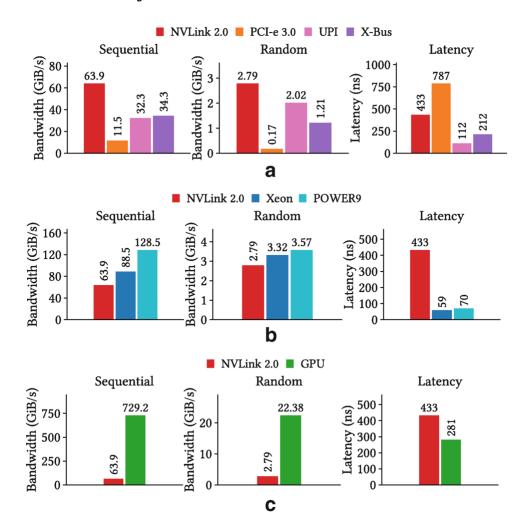

- 2.4 Processing Large Data on GPUs with Fast Interconnects

- 2.4.1 Analysis of Fast Interconnect

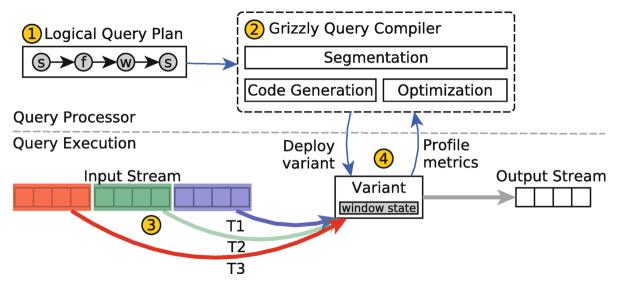

- 2.5 Efficient Stream Processing Through Adaptive Query Compilation

- 2.5.1 Query Compilation

- **2.5.2 Grizzly**

- 2.6 Conclusion

#### 3 Efficient Event Processing on Modern Hardware

Marius Kuhrt, Nikolaus Glombiewski, Michael Körber, Andreas Morgen, Dominik Brandenstein and Bernhard Seeger

- 3.1 Introduction

- 3.2 Preliminaries

- 3.2.1 Data Model

- 3.2.2 Operations

- 3.3 Related Work

| 3.4 System and Hardware Overvio | 3. | 4 | S | stem | and | Hard | lware | <b>Overv</b> | iev |

|---------------------------------|----|---|---|------|-----|------|-------|--------------|-----|

|---------------------------------|----|---|---|------|-----|------|-------|--------------|-----|

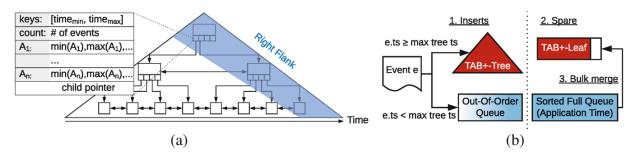

- 3.4.1 ChronicleDB

- 3.4.2 Java Event Processing Connectivity (JEPC)

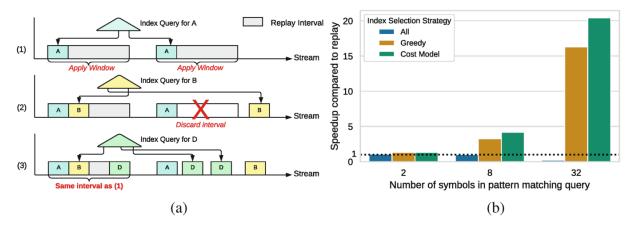

- 3.5 Event Pattern Matching

- 3.5.1 Index Acceleration

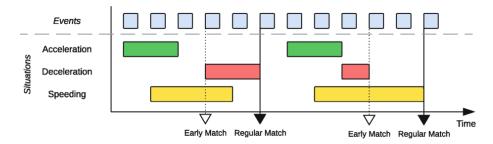

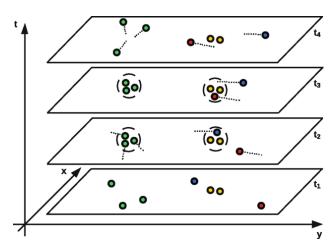

- 3.5.2 Situation Pattern Matching

- 3.5.3 Group Pattern Matching

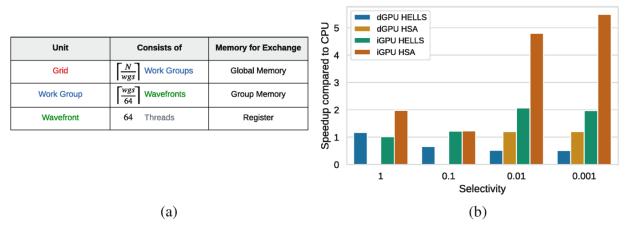

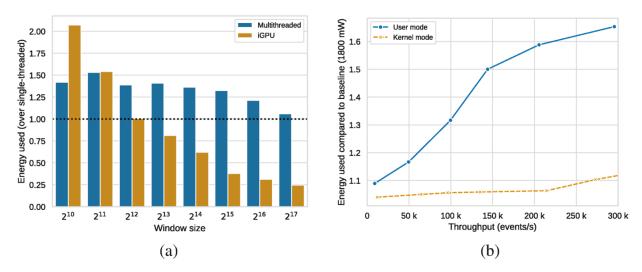

- 3.6 Energy Efficiency and iGPUs

- 3.6.1 HSA Facilities

- 3.6.2 Operators

- 3.6.3 Energy Efficiency

- 3.7 Compression

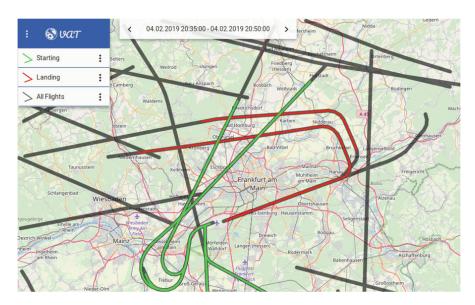

- 3.8 Applications

- 3.9 Conclusion and Outlook

## 4 Hybrid Transactional/Analytical Graph Processing in Modern Memory Hierarchies

Alexander Baumstark, Muhammad Attahir Jibril and Kai-Uwe Sattler

- 4.1 Introduction

- 4.2 Background

- **4.2.1 Persistent Memory Characteristics**

- 4.2.2 Property Graph Model

- **4.2.3 Temporal Graphs**

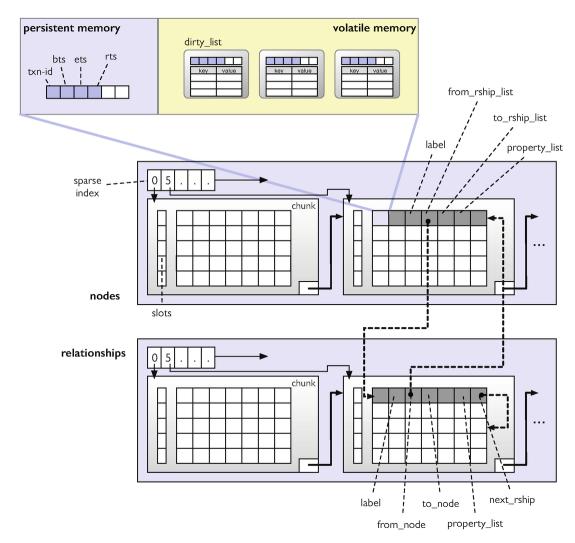

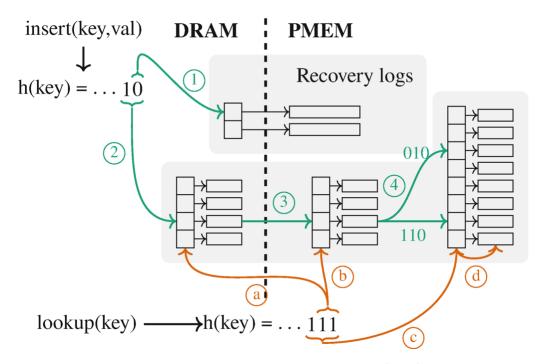

- 4.3 Data Structures for Transactional Graph Data in PMem

- 4.3.1 Design Goals

- **4.3.2 Data Structures for Graphs**

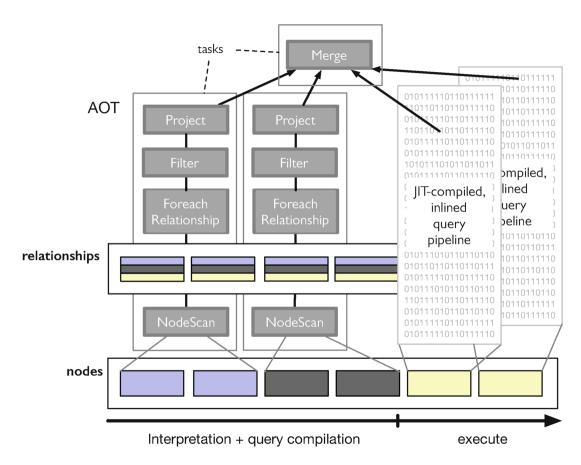

- 4.4 Graph Query Processing

- **4.4.1 Push-Based Approach**

- 4.4.2 Just-in-Time Query Compilation

- **4.4.3 Adaptive Query Compilation**

- **4.4.4 Query Recovery**

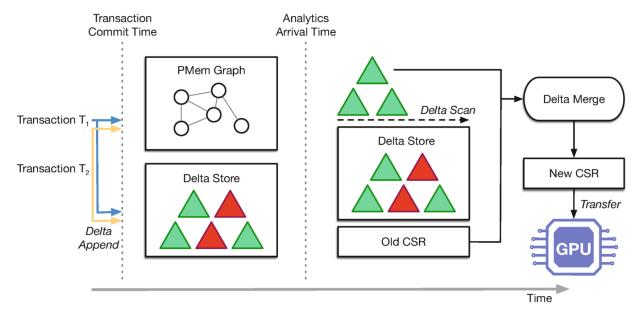

- 4.5 Graph Analytics on Transactional Data

- 4.5.1 Data Structures for Graph Analytics

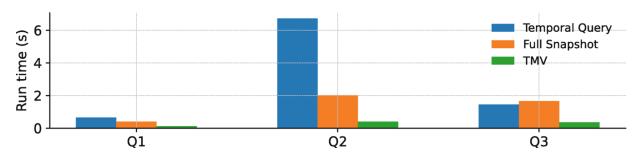

- **4.6 Exploiting the Storage Hierarchy for Time- Travel Queries**

- 4.6.1 Data Model

- 4.6.2 Temporal Query Processing

- 4.6.3 TMV Model

- 4.7 Related Work

- 4.7.1 PM-Aware Storage Design

- **4.7.2 Graph Database Management**

- 4.7.3 Temporal Graph Data Management

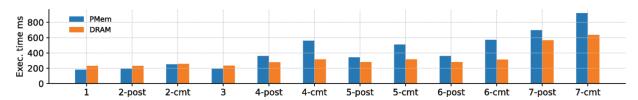

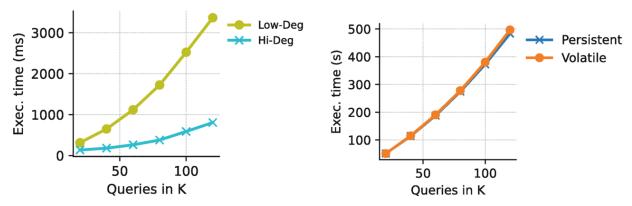

- 4.8 Evaluation

- 4.9 Conclusion

5 MxKernel: A Bare-Metal Runtime System for Database Operations on Heterogeneous Many-Core Hardware

Marcel Lütke Dreimann, Jan Mühlig, Michael Müller, Olaf Spinczyk and Jens Teubner

| 4   | -  |      | -  |     |               |

|-----|----|------|----|-----|---------------|

|     | In | tro  |    | CTI | $\mathbf{on}$ |

| • 4 |    | LL U | uu |     | UII           |

#### **5.2 Task-Based Parallelism**

- **5.2.1 Background**

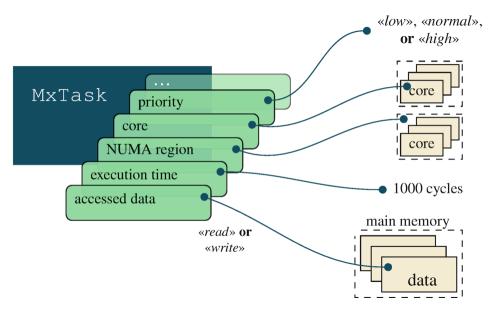

- **5.2.2 MxTask Abstraction**

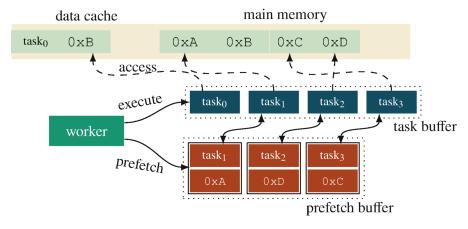

- **5.2.3 Annotation-Driven Prefetching**

- **5.2.4** Annotation-Driven Synchronization

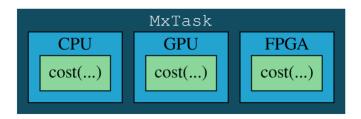

- **5.2.5** Annotation-Driven Heterogeneity

#### **5.3 Leveraging Tasks at the DBMS Layer**

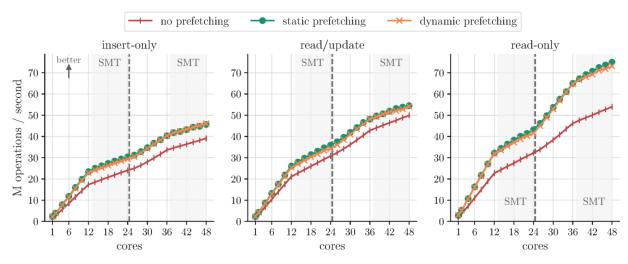

- 5.3.1 Building a Task-Based Blink-Tree

- **5.3.2 Experimental Evaluation**

## **5.4 Dynamic Resource Management with Tasks and Cells**

- 5.4.1 Background

- **5.4.2 State of the Art**

- 5.4.3 Enabling Swift Adaptation with the MxKernel

- **5.4.4 Experimental Evaluation**

- **5.5 Conclusion and Future Work**

#### References

## **6 Scaling Beyond DRAM Without Compromising Performance**

Lukas Vogel, Christoph Anneser, Ferdinand Gruber, Thomas Neumann, Jana Giceva and Alfons Kemper

- 6.1 Introduction

- 6.1.1 The Tough Reality

- 6.1.2 Our Contributions

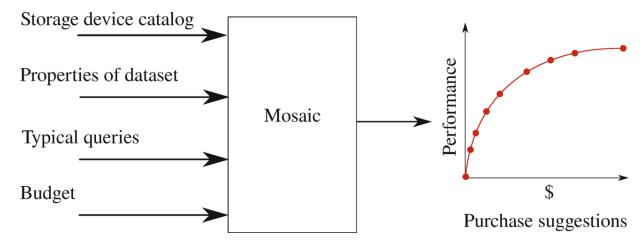

- 6.2 Mosaic

- **6.2.1 Placement Mechanism**

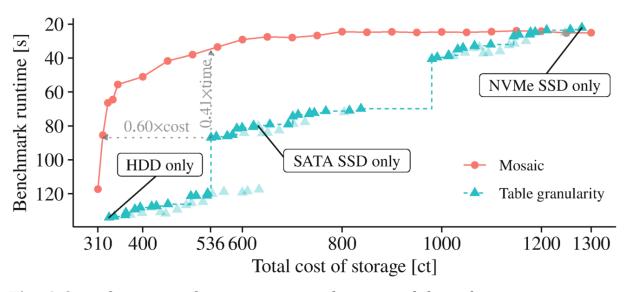

- **6.2.2 Evaluation**

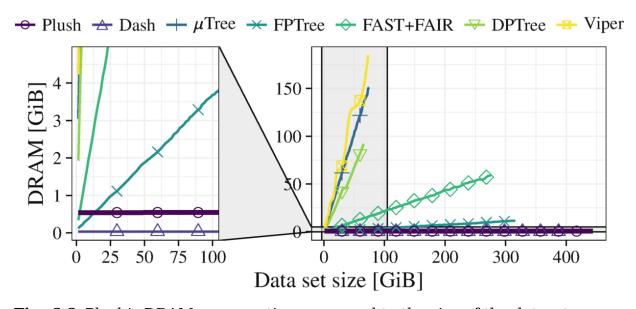

- 6.3 Plush

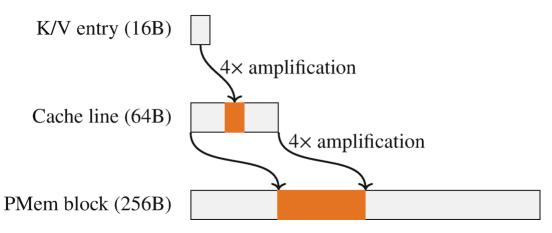

- **6.3.1 The Problem with Persistent Memory**

- 6.3.2 Architecture

- **6.3.3 Evaluation**

- **6.4 Programming Fully Disaggregated Systems**

- **6.4.1 Trends in Large-Scale Data Processing**

- **6.4.2 Design Principles**

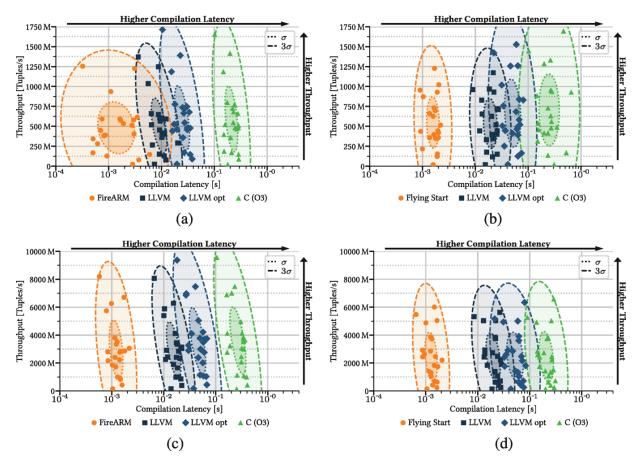

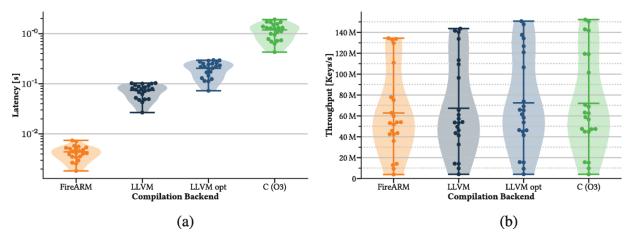

- **6.5 ARM: Code Generation for High-End and Edge Devices**

- **6.5.1 Query Compilation**

- **6.5.2 Embedded ARM Processors**

- **6.6 Conclusions**

# 7 ReProVide: Query Optimization and Near-Data Processing on Reconfigurable SoCs for Big Data Analysis

Tobias Hahn, Maximilian Langohr, Andreas Becher, Lekshmi Beena Gopalakrishnan Nair, Klaus Meyer-Wegener, Jürgen Teich and Stefan Wildermann

- 7.1 Introduction

- 7.2 Related Work

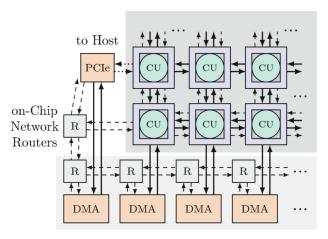

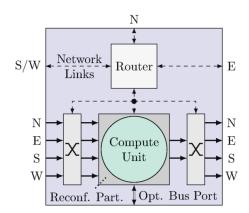

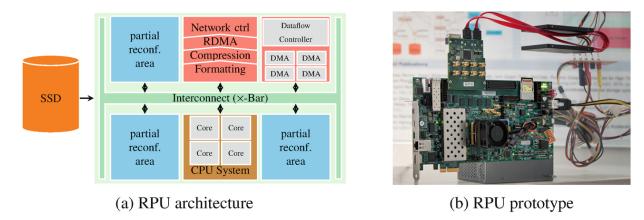

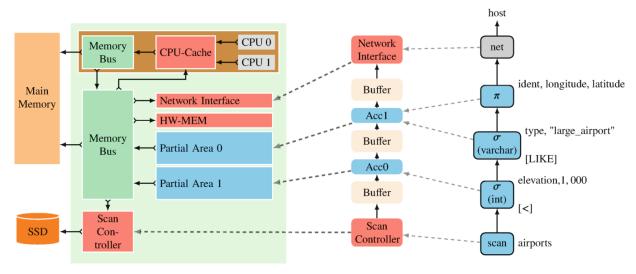

- 7.3 Heterogeneous Partially Reconfigurable Architecture for Near-Data Processing

- 7.3.1 Reconfigurable Data-Provider Unit (RPU)

Architecture

- 7.3.2 Determining a Query-Specific Configuration for RPUs

- 7.3.3 RPU-Supported Operators and Operations

- 7.3.4 Optimistic Filtering to Support Complex and Blocking Operators

- 7.4 Near-Data Processing of Streaming Data

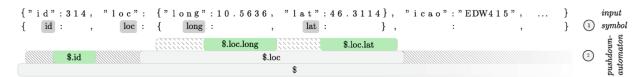

- 7.4.1 Raw Filtering for Optimistic Data-Stream Processing

- 7.4.2 Parse-Filter-Project: Selective Data-Stream Parsing

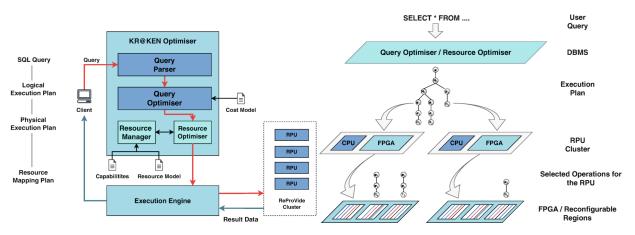

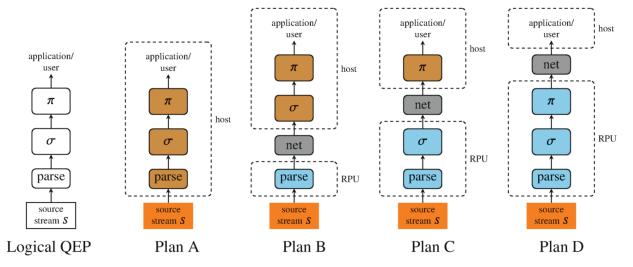

- 7.5 Query Optimization for Heterogeneous ReProVide Clusters

- 7.5.1 Holistic Query Optimization

- 7.5.2 Optimizing Relational and Stream-Based Queries for Heterogeneous Systems

- 7.5.3 Learning from the Past: Offline Optimization to Improve Query Optimization

- 7.6 Experimental Evaluation

- 7.7 Summary

8 Scalable Data Management on Next-Generation Data Center Networks

Matthias Jasny, Tobias Ziegler and Carsten Binnig

- 8.1 Introduction

- 8.2 Background

- **8.2.1** Remote Direct Memory Access (RDMA)

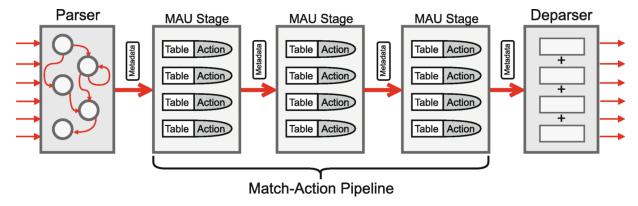

- **8.2.2 Programmable Switches**

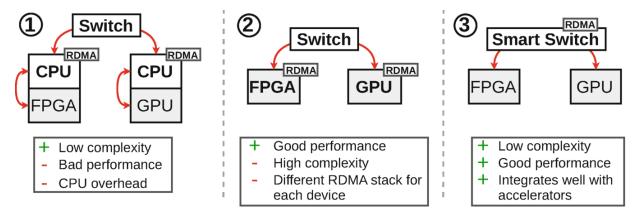

- **8.3 Scalable Data Management with RDMA**

- 8.4 P4DB: The Case for In-Network OLTP

- 8.4.1 Overview of P4DB

- **8.4.2 Experimental Evaluation**

- **8.4.3 Growing Hot-Sets Beyond Switch's Capacity**

- **8.4.4 Summary**

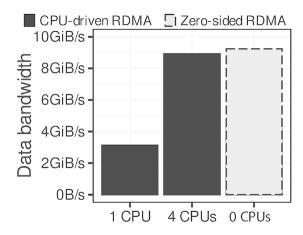

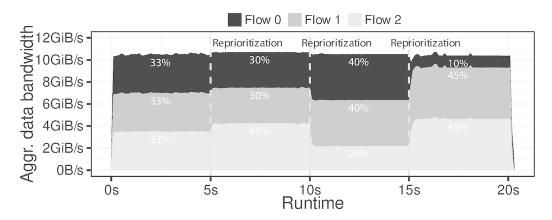

- 8.5 Zero-Sided RDMA

- 8.5.1 Overview of Zero-Sided RDMA

- 8.5.2 Switch vs. SmartNICs

- **8.5.3 Advanced Communication Flows in Zero-Sided RDMA**

- **8.5.4 Experimental Evaluation**

- **8.5.5 Summary**

- **8.6 Conclusion and Future Directions**

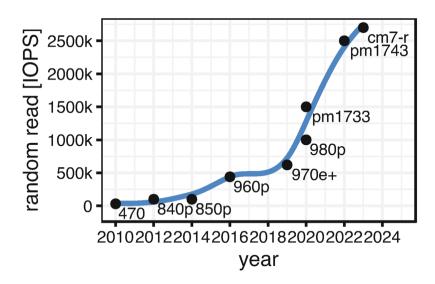

9 Managing Very Large Datasets on Directly Attached NVMe Arrays

Gabriel Haas, Adnan Alhomssi and Viktor Leis

- 9.1 Introduction

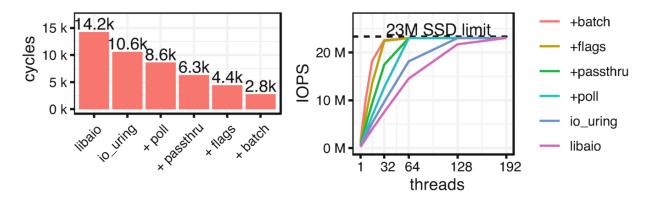

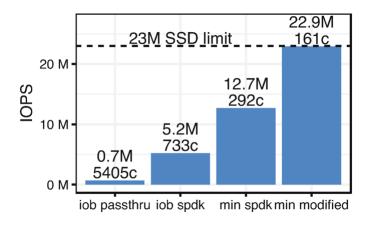

- **9.2 Slicing Through the I/O Stack Abstraction**Layers

- 9.2.1 Experimental Setup

- 9.2.2 Slicing Through the I/O Stack

- 9.2.3 Secret Flags in the Kernel Universe

- 9.2.4 A Lower Bound for I/O Handling

- 9.2.5 Thank God It's Fsynced: Durability

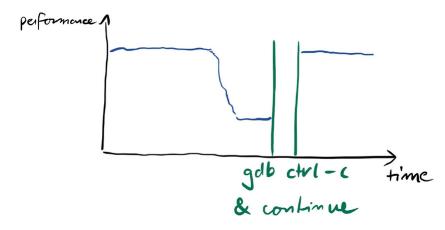

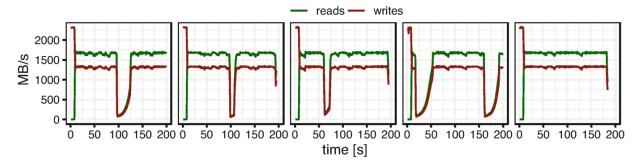

- 9.3 Benchmarking and Hardware Pitfalls

- 9.3.1 Don't Trust a Benchmark You Did Not Do Yourself

- 9.3.2 The Strange Case of the IOMMU and Its Root-Complex

- 9.3.3 Too Hot to Handle

- 9.3.4 The Shark

- 9.4 I/O in High-Performance Storage Engines

- 9.4.1 Visible Without Looking Glass

- 9.4.2 NVMe-Enabled Performance in Storage Engines

- 9.4.3 Exploiting New Kernel Features

- 9.5 Conclusion

#### **Contributors**

#### **David Broneske**

German Center for Higher Education Research and Science Studies, Hannover, Germany

#### Vitalii Burtsev

Hardware-Oriented Technical Computer Science, Faculty of Electrical Engineering and Information Technology, University of Magdeburg, Magdeburg, Germany

#### **Anna Drewes**

Hardware-Oriented Technical Computer Science, Faculty of Electrical Engineering and Information Technology, University of Magdeburg, Magdeburg, Germany

#### Thilo Pionteck

Hardware-Oriented Technical Computer Science, Faculty of Electrical Engineering and Information Technology, University of Magdeburg, Magdeburg, Germany

#### **Bala Gurumurthy**

Databases and Software Engineering, Faculty of Computer Science, University of Magdeburg, Magdeburg, Germany

#### **Gunter Saake**

Databases and Software Engineering, Faculty of Computer Science, University of Magdeburg, Magdeburg, Germany

#### Anastasiia Kozar

Technische Universität Berlin, Berlin, Germany

#### Janis von Bleichert

vB Internet GmbH, Berlin, Germany

#### Sebastian Breß

Snowflake, Inc., Berlin, Germany

#### Philipp M. Grulich

Technische Universität Berlin, Berlin, Germany

#### **Clemens Lutz**

NVIDIA, Santa Clara, CA, USA

#### Tilmann Rabl

HPI, University of Potsdam, Potsdam, Germany

#### Viktor Rosenfeld

Technische Universität Berlin, Berlin, Germany

#### **Jonas Traub**

Technische Universität Berlin, Berlin, Germany

#### Steffen Zeuch

Technische Universität Berlin, Berlin, Germany

#### Volker Markl

Technische Universität Berlin, DFKI GmbH, Berlin, Germany

#### **Marius Kuhrt**

University of Marburg, Marburg, Germany

#### Nikolaus Glombiewski

University of Marburg, Marburg, Germany

#### Michael Körber

University of Marburg, Marburg, Germany

#### **Andreas Morgen**

University of Marburg, Marburg, Germany

#### **Dominik Brandenstein**

University of Marburg, Marburg, Germany

#### **Bernhard Seeger**

University of Marburg, Marburg, Germany

#### **Alexander Baumstark**

Database & Information Systems Group, TU Ilmenau, Ilmenau, Germany

#### **Muhammad Attahir Jibril**

Database & Information Systems Group, TU Ilmenau, Ilmenau, Germany

#### **Kai-Uwe Sattler**

Database & Information Systems Group, TU Ilmenau, Ilmenau, Germany

#### Marcel Lütke Dreimann

Osnabrück University, Osnabrück, Germany

#### Michael Müller

Osnabrück University, Osnabrück, Germany

#### **Olaf Spinczyk**

Osnabrück University, Osnabrück, Germany

#### Jan Mühlig

TU Dortmund University, Dortmund, Germany

#### **Jens Teubner**

TU Dortmund University, Dortmund, Germany

#### **Lukas Vogel**

Technische Universität München, München, Germany

#### **Christoph Anneser**

Technische Universität München, München, Germany

#### Ferdinand Gruber

Technische Universität München, München, Germany

#### **Thomas Neumann**

Technische Universität München, München, Germany

#### Jana Giceva

Technische Universität München, München, Germany

#### **Alfons Kemper**

Technische Universität München, München, Germany

#### **Tobias Hah**

Friedrich-Alexander-Universität Erlangen-Nürnberg (FAU), Erlangen, Germany

#### **Maximilian Langohr**

Friedrich-Alexander-Universität Erlangen-Nürnberg (FAU), Erlangen, Germany

#### **Andreas Becher**

TU Ilmenau, Erlangen, Germany

#### Lekshmi Beena Gopalakrishnan Nair

Friedrich-Alexander-Universität Erlangen-Nürnberg (FAU), Erlangen, Germany

#### Klaus Meyer-Wegener

Friedrich-Alexander-Universität Erlangen-Nürnberg (FAU), Erlangen, Germany

#### Jürgen Teich

Friedrich-Alexander-Universität Erlangen-Nürnberg (FAU), Erlangen, Germany

#### Stefan Wildermann

Friedrich-Alexander-Universität Erlangen-Nürnberg (FAU), Erlangen, Germany

#### **Matthias Jasny**

Technische Universität Darmstadt, Darmstadt, Germany

#### **Tobias Ziegler**

Technische Universität Darmstadt, Darmstadt, Germany

#### **Carsten Binnig**

Technische Universität Darmstadt, Darmstadt, Germany

#### **Gabriel Haas**

Technische Universität München, Darmstadt, Germany

#### **Adnan Alhomssi**

RelationalAI, Erlangen, Germany

#### **Viktor Leis**

Technische Universität München, München, Germany

## 1. ADAMANT: Hardware-Accelerated Query Processing Made Easy

David Broneske<sup>1  $\boxtimes$ </sup>, Vitalii Burtsev<sup>2  $\boxtimes$ </sup>, Anna Drewes<sup>2  $\boxtimes$ </sup>, Bala Gurumurthy<sup>2  $\boxtimes$ </sup>, Thilo Pionteck<sup>3  $\boxtimes$ </sup> and Gunter Saake<sup>3  $\boxtimes$ </sup>

- (1) German Center for Higher Education Research and Science Studies, Hannover, Germany

- (2) Hardware-Oriented Technical Computer Science, Faculty of Electrical Engineering and Information Technology, University of Magdeburg, Magdeburg, Germany

- (3) Databases and Software Engineering, Faculty of Computer Science, University of Magdeburg, Magdeburg, Germany

#### ■ David Broneske (Corresponding author)

Email: broneske@dzhw.eu

⊠Vitalii Burtsev

Email: vitalii.burtsev@ovgu.de

**⊠Anna Drewes**

Email: anna.drewes@ovgu.de

**Bala Gurumurthy**

Email: thilo.pionteck@ovgu.de

**⊠Thilo Pionteck**

Email: bala.gurumurthy@ovgu.de

**⊠Gunter Saake**

Email: gunter.saake@ovgu.de

#### Abstract

We present ADAMANT, an adaptive data management architecture for evolving heterogeneous hardware/software systems. The ADAMANT system enables plug'n'play integration of co-processors such as GPUs and FPGAs, provides a unified runtime that supports cross-device parallelization of SQL query execution on arbitrary co-processors at runtime, and supports multi-query processing. We discuss the concepts behind and performance of ADAMANT following an example query (TPC-H Q6), present different execution models for cross-device execution, and provide an FPGA hardware architecture that allows the implementation of query-specific hardware accelerators at runtime. In addition, we introduce a new approach for approximate query processing for FPGAs. Our performance analysis concludes that the use of hardware accelerators and device-specific implementations of query operators as part of a common system can provide significant speedups over state-of-the-art query execution engines.

#### 1.1 Introduction

The database community faces the extreme challenge that the volume of data to be processed has increased exponentially in recent years. While the amount of data created, captured, copied, and consumed in 2020 was approximately 64.2 zettabytes, it is predicted that it will grow to more than 180 zettabytes by 2025 [42]. CPU-based database systems reach their performance and scalability limits with this amount of data, especially with regard to the memory wall, power consumption, and fast response times. This requires new approaches at the hardware and algorithm level, such as integrating co-processors into database systems or approximating query processing to lower response times.

The traditional approach to data analytics has been to process data in batches, often taking minutes or hours to yield results. This offline processing contrasts sharply with the goals of interactive analytics, which aims to deliver query responses within seconds, thereby enabling rapid hypothesis testing. Approximate query processing (AQP) has emerged as a solution, allowing database systems to provide aggregated responses to queries on large datasets in a timely way, thereby bringing us closer to the ideal of interactive analytics.

In order to speed up the exact response to database queries, the use of heterogeneous hardware architectures appears to be promising. In heterogeneous systems, CPUs are supported by specialized coprocessors such as Graphical Processing Units (GPUs) or Field Programmable Gate Arrays (FPGAs). The advantage of heterogeneous hardware systems is that multiple operations can be performed in parallel on different devices. Query operators can be mapped to the hardware device for which the most efficient implementation of an operator is available. However, these benefits are countered by significant challenges. First, a mechanism must be provided to integrate co-processors with their supported set of query operators into the database management system (DBMS), and second, all co-processors

require custom operator implementations to process the queries. In particular, the provision of operator implementations for a specific hardware device can be very time-consuming and requires domain knowledge.

To address these challenges, we developed ADAMANT, an adaptive data management solution for evolving heterogeneous hardware/software systems. ADAMANT allows new co-processors to be integrated without reworking other components of the query engine. This is supported by pluggable interfaces that encapsulate all interactions with co-processors and a unified runtime that handles execution on arbitrary co-processors, with a chunked execution model for scalable query processing.

We show the features, flexibility, and benefits of ADAMANT through Query 6 of the TPC-H benchmark [45] throughout this chapter. In particular, we will discuss the execution model of ADAMANT, which is based on (device-specific) primitives, the influence of the underlying hardware on an appropriate primitive realization, and how primitive fusion can increase efficiency. We will present an approach to produce hardware accelerators for arbitrary queries on an FPGA at runtime and discuss different execution models for cross-device execution of queries on CPUs and GPUs. In addition, we will present approaches for multiquery processing. For approximate query processing, an approach based on the concept of Bag of Little Bootstraps (BLP) will be discussed.

The rest of the chapter is organized as follows: Sect. 1.2 presents the overall structure of ADAMANT and discusses the specific challenges for realizing plug'n'play capabilities in DBMSs. Section 1.3 presents a novel approach to an FPGA-based approximate query-processing accelerator. The concept of device-specific primitives is introduced in Sect. 1.4, which is used to discuss the FPGA overlay architecture in Sect. 1.5 and the cross-device execution models in Sect. 1.6. Optimization possibilities for multi-query processing are presented in Sect. 1.7. The chapter ends with a conclusion in Sect. 1.8.

## 1.2 Challenges for ADAMANT's Plug'n'Play Architecture

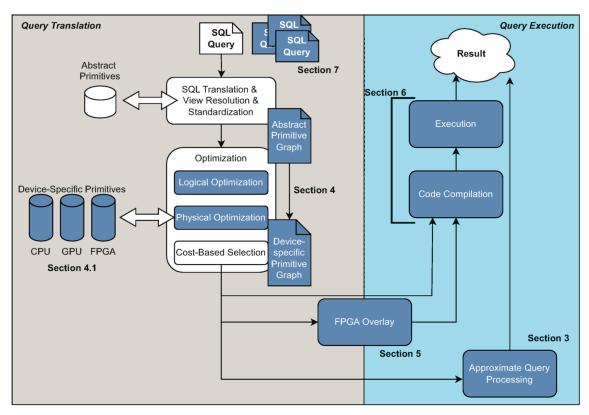

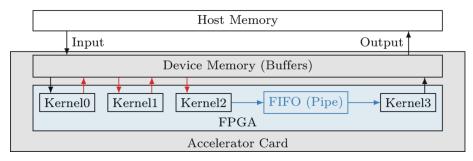

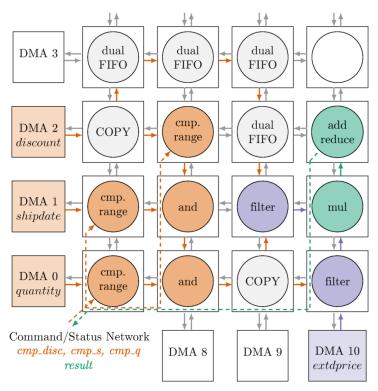

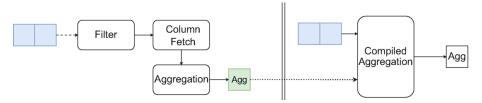

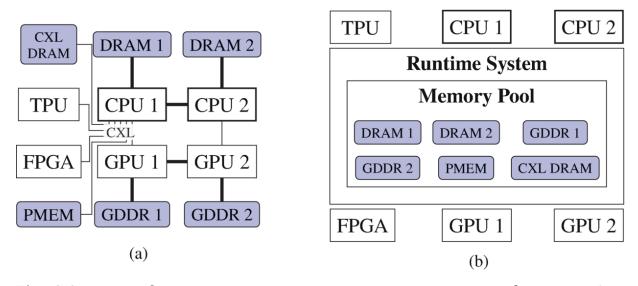

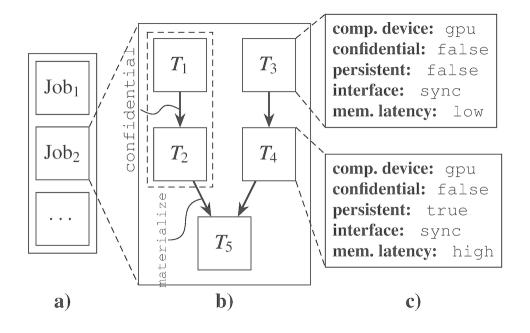

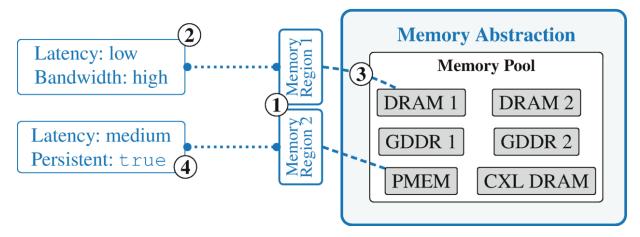

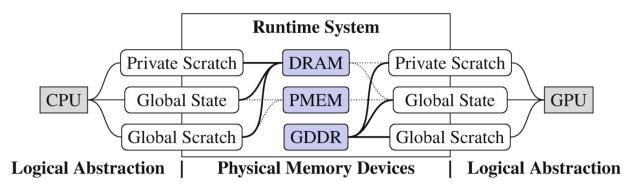

For an effective integration of modern heterogeneous processors into the query-processing pipeline, there are several adaptations necessary, each posing a specific challenge. The challenges are (C1) the tuning for device-specific processing capabilities, (C2) the exploitation of the full processing power, and (C3) the effective simultaneous execution of multiple queries at once. We exemplify necessary changes to the database system in Fig. 1.1 by using the standard database processing

workflow split into query translation and query execution [39]. In query translation, the SQL query is parsed and standardized, after which optimization takes place, which usually transforms the logical query graph into a physical optimized execution plan. This plan is then prospectively compiled and executed. In the following, we outline the necessary changes to this query-processing workflow in order to overcome the challenges.

*Fig. 1.1* Adapted query-processing workflow when incorporating heterogeneous co-processors in a plug'n'play fashion. White components represent unchanged steps, while blue components represent adaptations to the standard process

#### 1.2.1 C1: Device-Specific Processing Capabilities

Due to their task-based specialization, processors and co-processors provide different processing capabilities [6, 37, 38]. For instance, CPUs provide out-of-order execution and branch prediction, which is why they are best suited for latency-critical tasks. In contrast, GPUs offer massive data-parallel processing capabilities in a SIMT-fashion (single instruction, multiple threads), which is why they are optimized for throughput. FPGAs, on the other hand, can be programmed for any number of operations and sequences of operations. However, due to their limited space and lower clock-frequency, data parallelism is limited, and small pipelines cannot exploit the FPGA's advantages compared to CPUs or GPUs. As a result, the query plan (e.g., operator-

at-a-time processing on GPUs vs. pipelining on the FPGA) and also implementations of operators (branching on CPU vs. branch-free processing on GPU) differ per involved device.

Hence, we adapted the standard query-processing workflow by adding primitive definitions (suboperations of database operators introduced in Sect. 1.4) and respective code bases per device in our ADAMANT system. Hence, when co-processors are plugged in, also respective primitives optimized for the device have to be provided. Furthermore, physical optimization has to be extended to optimize for the dimension of choosing the right device-specific primitive. Moreover, our adapted query-processing workflow has a special step for configuring the FPGA overlay (see Sect. 1.5), which is a necessary step for incorporating the FPGA into the workflow.

#### 1.2.2 C2: Exploitation of Full Processing Power

When overcoming the first Challenge C1, the system is able to effectively incorporate different co-processors and efficiently execute a single query on a single device. Given the possibility to use arbitrary (co)-processors from a system, the challenge arises to put all (co)-processors concurrently into action. Specifically, the system would enable a distribution of subtasks and data chunks to the different devices and mind the memory restrictions of the devices. Furthermore, when using FPGAs, their configuration time may hinder their application because the resulting latency overshadows their performance benefits compared to other devices, which keeps this processing power unused.

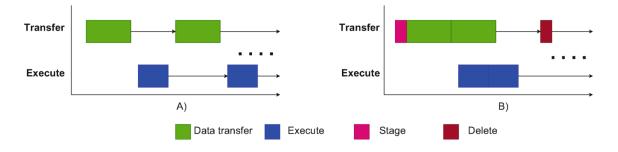

In order to overcome this challenge, we extend the query execution capabilities of the ADAMANT system by allowing to start executing the query processing in an interpreted fashion. This effectively hides any compilation or configuration time (see Sect. 1.6). Furthermore, we provide a chunking approach that allows for cross-device query execution and even executing larger-than-memory workloads.

#### 1.2.3 C3: Effective Parallel Execution of Multiple Queries

Due to our contributions for C1 and C2, we are now capable of executing a single query across different devices. However, the usual use case is to serve several user requests in parallel, leading to multiple queries being processed concurrently. The question is whether concurrently running queries with enough similarity can be optimized by sharing intermediate results when executing. This is a feature that would influence the final query plan and is, thus, impacting logical query optimization. Furthermore, since many users are on an exploratory search for data, their results do not always need to be 100

% exact. Hence, this is an additional optimization that could decrease the load on the system and lead to a better throughput when running multiple queries.

To this end, we investigate mechanisms to share and reuse results of concurrently running queries (see Sect. 1.7), where the impact of query similarity on the resulting performance needs to be regarded. Moreover, we propose an alternative approximate query execution for exploratory queries that do not need the exact query result (see Sect. 1.3).

#### 1.3 Approximate Query Processing

Approximate query processing (AQP) is essential for rapidly analyzing large datasets where traditional methods are inefficient due to high computational costs and long processing times. AQP strategies balance accuracy and performance by providing fast, though approximate, insight into the data. The following are the main AQP methodologies, each offering solutions to specific data analysis problems that we considered as a basis for developing our own solution.

#### 1.3.1 Approximation Approaches

The online aggregation method by Hellerstein et al. [25] introduces a technique that incrementally refines query results, enabling users to halt the process when results fall within an acceptable error range. This method facilitates interactive data analysis by offering initial rough estimates that progressively become more accurate, thereby considerably shortening the time to reach preliminary insights.

The Stratified Sampling approach, as showcased in BlinkDB [1] and VerdictDB [32], enhances AQP effectiveness by smartly dividing the dataset. This technique segments the dataset into uniform groups, from which samples are independently drawn, boosting sample representativeness, particularly in diverse datasets. The LAQy framework [40] improves stratified sampling by enabling efficient and adaptive sample reuse. It allows for partial reuse of samples by dynamically adjusting them based on the changing predicates of query workloads.

Machine Learning Models for AQP, illustrated by DBEst [30] and DeepDB [26], utilize past query behaviors and data features to anticipate query results. This sophisticated strategy employs machine learning's predictive capabilities to estimate query responses, notably lowering the computational demand by avoiding conventional exhaustive query evaluations.

The AQP++ framework, as developed by Peng et al. [33], introduces a transformative approach by synergizing sampling-based techniques

with aggregate precomputation (AggPre) for enhanced interactive analytics. This integration not only speeds up query answering by utilizing precomputed aggregates to refine estimates but also maintains unbiasedness and balances between speed, accuracy, and preprocessing costs. Key to its innovation is the inclusion of Bootstrap Methods for Error Estimation, which utilizes resampling to offer a robust framework for assessing the precision of AQP outcomes.

Bootstrapping [15] is a widely used statistical algorithm for the evaluation of data distributions in datasets. This technique creates a series of resamples from smaller subsets of the original dataset by repeated sampling with replacement. Because of its statistical foundation, bootstrapping is widely used in machine learning. However, bootstrap-based algorithms typically face a significant computational burden due to the resampling process. The size of the resamples in bootstrapping is comparable to the size of the original sample, contributing to the procedure's computational intensity.

#### 1.3.2 Bag of Little Bootstraps

The concept of bootstrapping in statistics involves generating numerous subsamples from the original dataset by resampling with replacement, to form an empirical distribution. This method allows for the estimation of the population distribution based on these subsamples. However, traditional bootstrapping requires processing a large number of data, resulting in significant computational demands, which limits its applicability in various fields.

To address the computational challenges of traditional bootstrapping, Kleiner et al. introduced the Bag of Little Bootstraps (BLB) algorithm [27]. This approach minimizes computational load by utilizing smaller subsamples for resampling and then scaling the results to match the size of the original dataset. This method significantly reduces the amount of data that needs to be processed, making the bootstrapping process more efficient with negligible compromising on accuracy.

When applying the BLB algorithm, a database query is executed on each resampled subset to obtain bootstrap estimates. These individual estimates are then averaged to derive an approximate answer to the original query. The BLB algorithm has demonstrated that to achieve a 95% confidence level in query answers, it is sufficient to use subsamples sized according to a specific formula, where the subsample size b is proportional to the original data size n as  $b = n^{\gamma}$  raised to a power  $\gamma$  between 0.6 and 0.9.

This scaling of subsample size, as recommended by the BLB algorithm, means that for a large dataset, the amount of data to be processed can be dramatically reduced, by orders of magnitude. For

example, for a dataset of one million values, only twenty to thirty subsamples of approximately four to sixteen thousand values would need to be processed to obtain reliable results, demonstrating the efficiency of the BLB algorithm in reducing computational requirements.

The BLB algorithm's approach to optimizing the balance between accuracy and computational burden by strategically selecting subsample sizes represents a significant advance in the field of statistics. By enabling efficient processing of large datasets while maintaining a high level of confidence in the results, the BLB algorithm offers a practical solution for a wide range of applications and has the potential to transform the way statistical analysis is conducted in large data environments.

#### 1.3.3 Streaming BLB

In order to address the computational demands of traditional bootstrapping and to bring bootstrapping to aggregate approximate query answering, we have developed our approach from standard BLB to allow streamed and pipelined data processing. Several important elements of the algorithm have been revised and replaced. In particular, Poisson bootstrapping [3, 35] allows stream data processing and reduces data transfer, using a method where a subset of distinct values is resampled, each multiplied by a Poisson-distributed coefficient as an estimate of the frequency of occurrence for that particular point in the resample. By crossing the BLB algorithm with Poisson-distributed resampling coefficients, the n-fold resampling of BLB is effectively transformed into a b-fold computation.

Figure 1.2 illustrates the Streaming BLB approach versus the traditional BLB method. In the naive BLB, an entry is selected randomly n times from a subsample of size b, requiring n memory accesses per resample. Each entry's representation in the resample, indicated by a numerical value next to each group, shows the resampling coefficient, which varies across resamples. The right side shows the Streaming BLB method, where resampling coefficients  $k_i$  are derived from a distribution, often approximated by a Poisson distribution with  $\lambda=n/b$ , facilitating the generation of b random numbers. For large  $\lambda$ , the Poisson can be approximated with a normal distribution (  $\mu=\lambda$ ,  $\sigma=\sqrt{\mu}$  ). Data normalization ensures total resampling coefficients match the original data size n.

Fig. 1.2 Naive bootstrapping (left) vs. Streaming BLB (right) [8]

The original BLB algorithm lacks data streaming capabilities. Streaming BLB overcomes this by allowing data streaming through its coefficient-based bootstrapping method, enabling parallel processing and hardware acceleration. Yet, this method demands a high-performance generation of random variables with specific probability distributions.

# 1.3.4 FPGA-Based Bag of Little Bootstraps

Taking into account all the advantages of BLB described above and our modifications to make this algorithm more applicable to accelerators, we chose FPGAs as the test platform. On the one hand, FPGAs offer pipelining and parallelization capabilities that are unmatched by other systems. On the other hand, they are very efficient in terms of power consumption.

# 1.3.4.1 Gaussian Random Number Generation (GRNG) on FPGAs

The efficient generation of random numbers with a given distribution is critical to the overall performance of the BLB streaming approach. Several strategies [2, 28, 44] balance performance with resource demands, with the Multihat [31] algorithm standing out for its efficiency in streaming resampling, producing a random number each clock cycle. It alters the probability density of uniformly distributed random numbers using additional bits and multiplexers, closely approximating a Gaussian distribution with an  $8\sigma$  tail accuracy. The Streaming BLB

method reduces the need for true random numbers by aligning the resampling rate with the expected probability distribution.

# 1.3.4.2 BLB Block Design

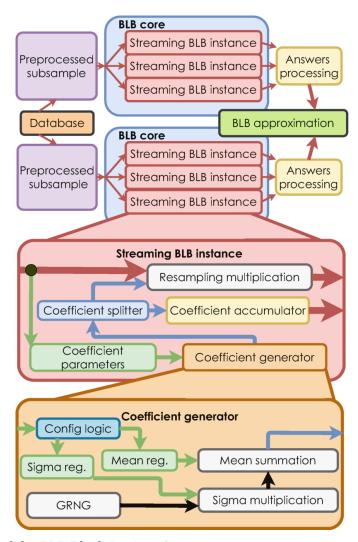

The overall structure of the BLB hardware accelerator is shown in the top part of Fig. 1.3. Each BLB core processes one subsample per time step, while the number of resamples per time step is determined by the number of streaming BLB instances. For each subsample, the individual query response is determined outside the BLB core in a preprocessing step that produces row-wise subsample results, either on CPU or on FPGA. In a post-processing step, the CPU aggregates the results of the individual BLB cores derived from a combination of resamples and subsample counts.

Fig. 1.3 Structure of the BLB Block Design [8]

The middle part of Fig. 1.3 shows the structure of a BLB streaming instance, which is responsible for resampling the data. A coefficient generator produces a random value every clock cycle, split for query multiplication and output normalization, ensuring coefficient sums align with the original dataset size. Parameters for the coefficient generator are obtained from the same stream as data for resampling.

The bottom part of Fig. 1.3 shows details of the coefficient generator, with Gaussian values x set to  $x' = \sigma x + \mu$ . The Multihat GRNG provides a random number for each cycle, supporting a flexible design for alternative generators. Configuration values define resampling coefficient distribution parameters for processing in Streaming BLB.

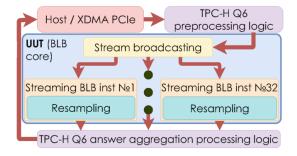

#### 1.3.5 Test Setup

For evaluation, we tested the performance of the BLB streaming approach for TPC-H Q6 [45] with subsamples on different scale factors (1–100) as an example of a data-intensive query with a heavy aggregation load. The testing was done on a Xilinx ZC706 board with a Zynq-7000 SoC FPGA, running at 125 MHz. For performance evaluation, the FPGA solution is tested against an Intel Core i7-6850K (12 threads, 4 GHz) CPU and an AMD Ryzen 7 5800X (16 threads, 3.6 GHz) CPU. Data storage is facilitated by a Patriot Burst SATA III 2.5" SSD.

The FPGA test system is shown in Fig. 1.4. Subsamples are created on the host CPU and then transferred to the FPGA where the query result for each subsample is computed. The results are then passed to the BLB unit. Here, subsample entries are multiplied by resampling coefficients, and data is aggregated at the output stage. When subsample processing is complete, the system prepares output data and sends it to the host.

Fig. 1.4 Test system structure [8]

The Xilinx DMA/Bridge Subsystem for PCI Express facilitates data transfers via the PCIe interface on the ZC706 accelerator board, which supports two AXI4-Stream channels. Consequently, it can host up to two BLB cores, while the number of resampling threads can scale with the

FPGA's capacity, reaching 64 in our setup. For processing TPC-H Q6, the FPGA handles extra arithmetic operations, including comparisons, additions, and multiplications, utilizing 32-bit floating-point arithmetic for enhanced precision and optimization opportunities. This implementation leverages the LOGIcore Floating Point v7.1 [46] IP core for streamlined data processing across the AXI4-Stream interface.

The system's result-processing logic comprises a multiplexer that compiles data packets from the resampling streams, answer accumulators, and normalization coefficients. These packets are then dispatched to the host via PCI Express XDMA for final processing and answer generation (Table 1.1).

Table 1.1 Zyng XC7Z045 SoC resource utilization

|          | 2 BLB cores          | One resampling |  |  |

|----------|----------------------|----------------|--|--|

| Resource | <b>Utilization %</b> | BLB instance   |  |  |

| LUT      | 78.19                | 2 977          |  |  |

| LUTRAM   | 23.92                | 357            |  |  |

| FF       | 57.83                | 3 587          |  |  |

| BRAM     | 6.69                 | 0              |  |  |

| DSP      | 64.44                | 9              |  |  |

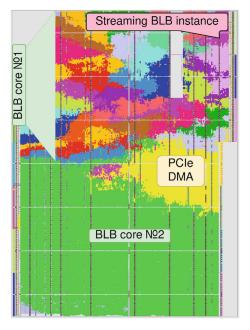

Figure 1.5 illustrates the layout of Streaming BLB instances within the BLB core. Each core consists of 32 Streaming BLB instances. The diagram highlights a full BLB core in green on the bottom. At the same time, the upper side displays another core, segmented into 32 individual Streaming BLB instances, each represented by a different color, such as the pink section in the upper right. The logic for processing TPC-H Q6 is positioned left from the yellow PCIe DMA block. Due to FPGA resource constraints, the system supports a maximum of 32 Streaming BLB instances per core.

Fig. 1.5 Logic placement on Zynq XC7Z045 SoC [8]

The CPU-based reference algorithm is developed in C++ using GCC v11.3.0 on Ubuntu 22.04. Its performance significantly depends on the choice of Gaussian random number generator. We explore this by comparing the standard C++ library's GRNG and the Ziggurat algorithm from the GNU Scientific Library [17]. For parallel execution, we employ OpenMP v4.5 [9].

#### 1.3.6 Evaluation

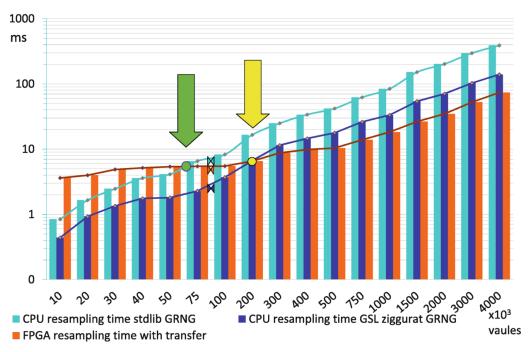

We evaluate the performance of the streaming BLB algorithm for the TPC-H Q6 query on both FPGA and i7-6850K CPU platforms, as shown in Fig. 1.6. As discussed in Sect. 1.3.2, the subsample size depends on two values. The first is the number of values in the dataset (scale factor, SF) and  $\gamma$ . We choose the TPC-H dataset with SF1 and  $\gamma=0.6$ , resulting in  $10\cdot10^3$  values as the leftmost point on the graph. The rightmost point corresponds to a set of subsamples created from a dataset with SF100 and  $\gamma=0.75$ , resulting in  $(\sim\!4000\cdot10^3)$  values.

Fig. 1.6 Execution time for TPC-H Q6 varying data size in log scale [8]

The CPU's setup includes a single BLB core with eight Streaming BLB instances across CPU cores. Similarly, the FPGA setup consists of one BLB core and eight Streaming BLB instances. The FPGA, however, could support more cores and instances with negligible overhead. FPGA time measurements account for PCIe data transfer delays.

Our results indicate that the CPU performs better for smaller datasets, but FPGAs excel as data size increases, surpassing CPU around 60,000 entries (see green arrow), showcasing FPGA's resampling efficiency. The CPU performance, which relies heavily on generating normal distributions, improves with the Ziggurat generator from the GSL library but still lags behind FPGA performance at about 200,000 entries, as shown by the yellow arrow.

The analysis underscores the superior efficiency of the FPGA even with modest data volumes, with CPU limitations primarily due to random number generation. Initially, FPGA's performance is hampered by PCIe setup times, which diminishes with larger datasets. Eventually, the FPGA's constraint shifts to its interface bandwidth, achieving twice the speed of the best CPU setup at 40 million entries, as evidenced by the logarithmic scale comparison.

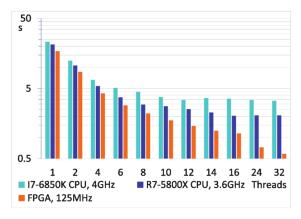

Figure 1.7 displays the Streaming BLB algorithm's execution time for TPC-H Q6, analyzing a 6 billion entry dataset, roughly 1 TB. With s=10 subsamples and r=100 resampling iterations per subsample, as recommended by Kleiner et al. [27] for 95% accuracy, the subsample size is around one million entries (15.3 MB). The FPGA consistently

outperforms the CPU in single-threaded operations, maintaining this advantage against the newer R7-5800X CPU.

Fig. 1.7 Execution time over threads [8]

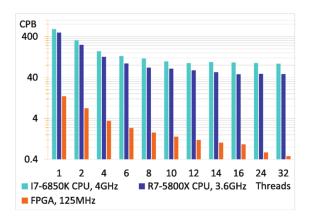

Figure 1.8 illustrates the Clocks Per Byte (CPB) efficiency with varying Streaming BLB instances under the same setup as prior measurements. This comparison helps evaluate how the number of instances affects the efficiency of the algorithm. Despite its high clock speed, the CPU requires many cycles for random number generation, a challenge solved by the FPGA in one clock cycle. The Ryzen CPU reaches its peak efficiency at 16 threads with a CPB of approximately 48, showcasing the algorithm's scalability with increased parallelism. In contrast, the FPGA's efficiency, constrained only by resource availability, is significantly higher, achieving about 50 times more efficiency than the CPU, even considering the logarithmic scale. Given the 32-bit data processing, the ideal FPGA efficiency would be  $\mathrm{CPB} = 0.25$ . However, due to PCIe XDMA transfer overheads, the achieved efficiency is  $\mathrm{CPB} = 0.58$ .

Fig. 1.8 Clock Cycles per Byte [8]

### 1.3.7 Conclusion

We presented an FPGA-based architecture for approximate query-processing acceleration. It relies on a Streaming BLB algorithm for efficient resampling. This approach significantly reduces data transfer, addressing the common bottleneck of data transfer rates in processing accelerators. The FPGA implementation shows a higher performance (from 2 times) compared to CPUs at moderate to large sample sizes, including data transfer times. Compared to CPUs, FPGAs are more efficient at generating random numbers based on multihat algorithm.

# 1.4 Device-Specific Primitive Graphs

The usual execution unit in traditional database systems is on the granularity of operators. However, given the Challenge C1 of exploiting device-specific computing capabilities, the operator level is too complex and broad to give a device-specific implementation per new device. This is why we introduce the concept of primitives and their tuning in the following sections.

#### 1.4.1 Primitives

#### 1.4.1.1 Motivation

One of the key motivations for tuning algorithms for different modern processors is the diversity in their processing capabilities. Specifically, modern devices support different paradigms of parallelism and have dedicated hardware units for efficient parallel execution. For example, a GPU supports massive data-parallel execution via multiple lightweight cores. On the other hand, FPGAs support the execution of deep processing pipelines. Hence, with devices supporting different levels of parallelism, we must also investigate ways to exploit their capabilities for faster database operations [19].

In order to minimize the implementation efforts as well as to explore the different device capabilities, database operators are split into granular functions that can be reused across multiple database operators, known as primitives [24]. Many researchers have proposed as well as investigated primitives of database operators for coprocessors [5, 34]. In our ADAMANT project, we have surveyed these existing primitives and used them for creating a primitive-based query execution plan.

# 1.4.1.2 Survey of primitives

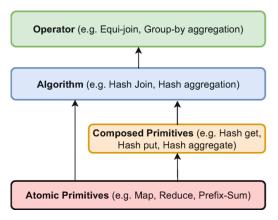

Based on our survey, we identify various granularities of primitives, which we show in Fig. 1.9: atomic, composed, algorithms, and finally the database operators.

Fig. 1.9 DBMS primitives in hierarchy based on [19]

Atomic primitives, such as map, reduce, and prefix sum, consist of a single processing loop with internal functional statements that cannot be split further. A composed primitive uses one or more atomic primitive or extends a primitive with custom implementations. Hash-build or hash-probe are examples of a composed primitive. A hash build, for example, can be built with a map primitive for the hash function to compute the target location and custom hashing technique implementation (like linear probing, cuckoo hashing) for placing the input in the hash table. Finally, these atomic and composed primitives can be used to run a complete database operator. A detailed list of these primitives is given in [19].

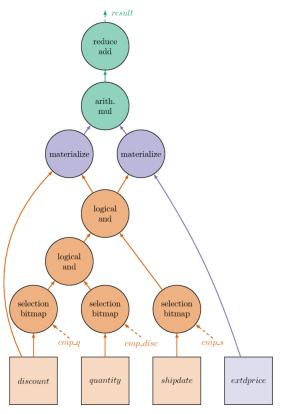

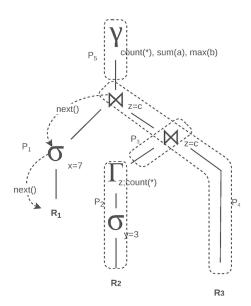

On the example of Q6, we can use the abovementioned primitives to define its query execution plan as given in Fig. 1.10. This plan is flexible w.r.t. execution, such that the selection primitives can be executed on the CPU with the materialize primitive executed on the GPU. This allows for tandem execution across different co-processors.

Fig. 1.10 A primitive-based query execution plan for TPC-H Query 6

In summary, due to the divide-and-conquer implementation style of primitives, these granular primitives minimize the implementation efforts as well as allow for exploring optimization opportunities. Using these definitions, we can freely plug in any device-specific implementation of a primitive without reworking the database operators. In upcoming sections, we show the ways to realize implementation of these primitives.

# 1.4.2 Grouped Aggregation as Device-Specific Primitive 1.4.2.1 Motivation

Though primitives allow re-usability of functionalities, we still need expertise about the underlying co-processor architecture to realize an optimal primitive implementation. Depending on the capability of the device, a particular implementation and its relevant parameter set might lead to optimal performance [38]. In this section, we take one such case of optimizing a device-specific primitive for processing a group-by aggregation using GPUs.

Group-by is most commonly implemented using hashing techniques, which group the input into buckets including an on-the-fly aggregation. The hashing techniques, however, incur a lot of random memory access due to the nature of the hash function when grouping the values.

Though such random accesses have minimal effects on CPUs and can be handled by the cache hierarchy [36], they will have severe effects for GPUs. Hence, we explore the alternative of using a sorting-based technique for group-by aggregation in GPUs.

Sorting has been a ubiquitous operation in query execution. Once sorted, the groups in the input are already arranged in a continuous sequence. In such sequences, resultant aggregation is computed in a single pass. However, such a sequential pass over an array of data needs to be efficiently partitioned among threads in a GPU, with all threads aggregating their respective value.

#### 1.4.2.2 Method

To aggregate values from concurrent threads, various software-based synchronization mechanisms are used. Modern GPUs (like NVIDIA GTX 1050) offer direct hardware support via atomic instructions to simplify such synchronization. These instructions serialize aggregation on a particular target, ensuring the correctness of results. Still, using atomics reduces execution performance as it increases the concurrency of the threads (see [22] for related experiments). Hence, we must implement an atomics-based aggregation technique that uses minimal atomics to get better performance. To this end, we propose two main techniques: (1) private aggregate variable and (2) private aggregate array.

# 1.4.2.3 Minimizing Atomics Using Private Space

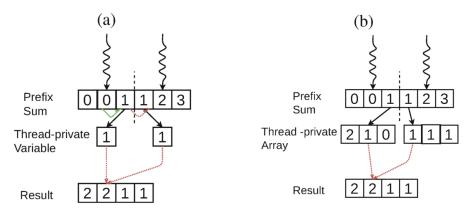

Since the input is sorted, we can exploit their sequence to reduce the overall atomics instructions executed. We achieve this by chunking the input such that all values of a single group are assigned to a single thread. In case multiple groups are present in a chunk, atomics are issued to store their partial aggregates. We store these partial aggregates using thread-private variables or arrays so that aggregated via an atomic instruction only when necessary. Both versions are shown in Fig. 1.11, where two threads aggregate their own chunk of three values.

$\emph{Fig. 1.11}$  Using private address space in GPU for storing partial aggregates. (a) Private aggregate variable. (b) Private aggregate array

The execution flow of both variants is roughly the same. In both, a thread sequentially reads its chunk of the prefix-sum and aggregates the corresponding input values within its private space until it encounters a group boundary. However, the variants differ in handling their partial aggregates and thus in the number of required atomics.

#### 1.4.2.4 Evaluation

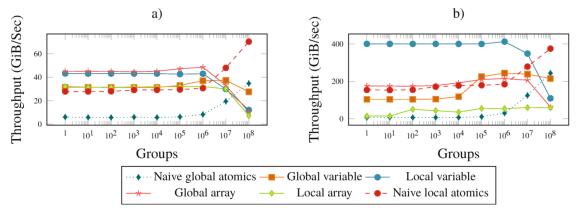

We compare the performance of the best-performing chunk and threadsize combination of the two private aggregate variants with the naive atomic variants with an optimal thread size on the two consumer GPUs GTX 1050Ti and RTX 2080Ti (see [21] for the choice of best-performing variants). The results are shown in Fig. 1.12.

$\emph{Fig. 1.12}$  Performance profile for hardware-aware aggregation variants. (a) GTX 1050Ti. (b) RTX 2080Ti

The variants in Fig. 1.12 are named as Naive representing the simple atomic aggregation without the variants, global/local represent the target memory, and variable/array represent the data structure for intermediate storage.

Our results indicate that the global array and local variable have higher throughput than the naive atomic variants for almost all numbers of groups (i.e., except a larger number of groups). This limitation of our variants is expected, as a larger number of groups leads to multiple groups within a chunk. In this case, a thread has to repeatedly insert the final result into global memory, degrading its performance. We also see only a small improvement in using local memory for our variants on the GTX 1050Ti, which in contrast is a considerable improvement on the RTX 2080Ti. Finally, for very high amounts of groups, the overhead of internal synchronization for the private aggregate variants does not pay off. Hence, naive local atomics performs best in this case.

#### 1.4.2.5 Conclusion

Our variants reach a speedup of 6x-12x to the naive atomics and 1.5-2.6x to the naive local memory atomics. For GTX 1050Ti, the variant using a private array in global memory is optimal with a speedup of 6x the naive atomics and 1.6x the naive local memory atomics. For RTX 2080Ti, the variant using a local variable is clearly superior with a speedup of about 12x the naive atomics and up to 2x the local memory atomics.

#### 1.4.3 Primitive Libraries

A handwritten primitive can be optimized based on the underlying device for best performance. However, as shown in the previous section, we need extensive evaluation as well as expertise of the underlying device to come up with such an implementation. Alternatively, we can also use pre-written libraries from device experts that circumvent such extensive implementation and evaluation setups.

#### 1.4.3.1 Motivation and Method

These device-specific libraries are general-purpose and support multiple generations of a co-processor out of the box. Additionally, these libraries add wrappers to device-specific implementations that hide the internal details from the end user. Thus, the user does not need to be an expert on the underlying device. In this context, we are looking into the support of such GPU-based libraries for database workloads. Based on our findings, we identify three libraries (ArrayFire, boost.compute, Thrust) that have partial support for database operations. These libraries and their implementation options for different database operators are given in Table 1.2. Overall, the most common database operators and primitives are supported by different libraries. However, especially joins are not yet supported. More information about the

library support in GPUs and their extensive evaluation with TPC-H queries can be found in [43].

**Table 1.2** Mapping of library functions to database operators

|                           | ArrayFire |                               | boost.compute |                                           | Thrust  |                                           |

|---------------------------|-----------|-------------------------------|---------------|-------------------------------------------|---------|-------------------------------------------|

| Database operators        | Support   | Function                      | Support       | Function                                  | Support | Function                                  |

| Selection                 | +         | where(operator())             | ~             | transform() & exclusive_scan() & gather() | ~       | transform() & exclusive_scan() & gather() |

| Nested-<br>Loops Join     | -         | -                             | +             | for_each_n()                              | +       | for_each_n()                              |

| Merge Join                | _         | _                             | _             | _                                         | _       | _                                         |

| Hash Join                 | _         | -                             | _             | -                                         | _       | -                                         |

| Grouped aggregation       | +         | sumByKey(),<br>countByKey(),  | +             | reduce_by_key()                           | +       | reduce_by_key()                           |

| Conjunction & disjunction | +         | setIntersect(),<br>setUnion() | +             | bit_and < T > (),<br>bit_or < T > ()      | +       | bit_and < T > (),<br>bit_or < T > ()      |

| Reduction                 | +         | sum < T > ()                  | +             | reduce()                                  | +       | reduce()                                  |

| Sort by key               | +         | sort()                        | +             | sort_by_key()                             | +       | sort_by_key()                             |

| Sort                      | +         | sort()                        | +             | sort()                                    | +       | sort()                                    |

| Prefix sum                | _         | -                             | +             | exclusive_scan()                          | +       | exclusive_scan()                          |

| Scatter & gather          | -         | -                             | +             | scatter(),<br>gather()                    | +       | scatter(),<br>gather()                    |

| Product                   | +         | operator*()                   | +             | transform() & multiplies < T > ()         | +       | transform() & multiplies< T>              |

+full support, ~partial support, - no support

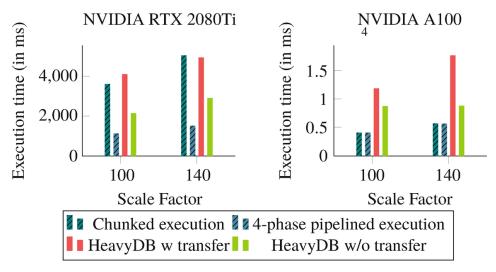

#### 1.4.3.2 Evaluation

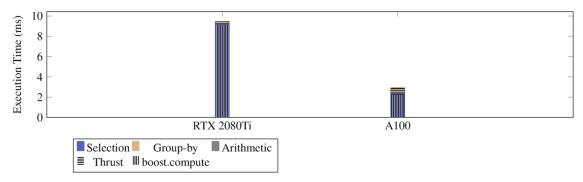

Using the three libraries, we can now execute TPC-H Q6 as per the query plan in Fig. 1.10. The performance of Q6 with TPC-H scale factor (SF) 1 using these libraries is plotted in Fig. 1.13. Our microbenchmark shows a poor performance from ArrayFire compared to boost.compute and Thrust [43]. Hence, we consider these for a complete query execution. Furthermore, due to its small runtime, the arithmetic step is not visible in the execution of Q6. Our results show that selection takes a considerable time compared to aggregation in the overall query execution. Even with the fast-performing library for the individual operators, we only get poor performance from using libraries. Additionally, we see a performance jump from using A100, but even in this case, the relative performance of selection is higher than

aggregation. Overall, the results show that the libraries are not tuned for database workload and must be code-optimized for better execution.

Fig. 1.13 Performance of TPC-H Q6 using GPU libraries

#### 1.4.3.3 Conclusion

Though these libraries support easy integration of alternative primitive implementations, they still lack complete support for databases. We summarize our findings for the library support for database operations in three dimensions:

- **Usefulness**: The usefulness of libraries for DBMS is fairly restrictive. Not all database operations are supported out-of-the-box through these libraries.

- **Usability**: Not all library functions are performance efficient. For optimal performance, a developer must test different libraries and combine their operators based on the query.

- **Portability**: Libraries can be executed across various devices out-of-the-box with fewer rework.

#### 1.4.4 Primitive Fusion

#### 1.4.4.1 Motivation

When executing tasks in a primitive-based system, common combinations of primitives might occur. These are of special interest for optimization, since planning with and scheduling and execution of a multitude of primitives allows dispatch overheads to accumulate drastically. Using code fusion to automatically implement Composed Primitives allows the system to take advantage of this potential and to better adapt to evolving circumstances without requiring humans in the loop. In addition to directly reducing the system overhead during execution, fused primitives offer also more optimization potential to the underlying (compiler or synthesis) tool chain. Finally, if the system has available Composed Primitives for commonly occurring subgraphs of query graphs, higher-level optimization and planning functions are simplified, as query graphs are reduced in size.

The per-primitive optimization potential is especially interesting for FPGAs, since during implementation of a circuit, the tool chain has access to every element, which allows for much more thorough optimizations across component boundaries than for software [4]. Also, each primitive must contain the logic required to interface with the rest of the accelerator system.

#### 1.4.4.2 Method

For successful adoption of primitive fusion into a primitive-based system, two abstract problems need to be solved: First, from a set of query plans, common subgraphs need to be identified. Second, during runtime, incoming queries need to be analyzed and instances of Composed Primitives need to be identified. As both of these problems are NP-hard, we propose a non-optimal but best-effort approach [12].

For the first problem, we propose a constructive greedy approach guided by a heuristic. Iteratively, the pair of primitives that is estimated to be most commonly replaced by the resulting Composed Primitive in the input set of queries by the heuristic is selected for fusion. The set of query graphs induced by this replacement is then taken as input for the next iteration. The advantage of this approach over taking the most commonly occurring combination is that due to the often treelike interconnections in the input graphs, not all instances can be replaced.

For the matching process at runtime, we propose another greedy approach, namely, iteratively matching the largest possible Composed Primitive in the topologically sorted query graph. This process should be fuzzy, since it can make sense to replace a subgraph of a query with a Composed Primitive doing additional work if the estimated runtime is lower.

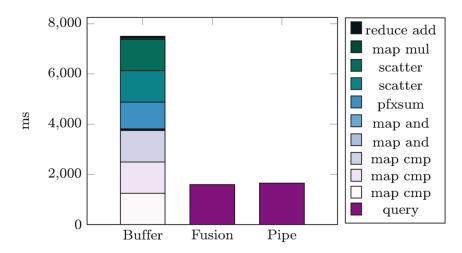

#### 1.4.4.3 Results

Evaluating the proposed algorithms for a set of TPC-H query graphs and a library of streaming primitives for FPGA resulted on average in a reduction of 47% in terms of FPGA resource use without any change in throughput [12]. TPC-H Query 6, for example, is reduced to only three Composed Primitives and one filter primitive implementing materialization. Due to the reductions in resource use, additional computations could be mapped to the FPGA. In the set of queries considered, the proposed heuristic chose the optimal candidates in 86% of the 21 iterations, more than three times more accurate than the naive approach [12].

# 1.5 FPGA Overlay Template

In this section, we describe the FPGA component of the ADAMANT system. After discussing the advantages and challenges of integrating FPGAs into a heterogeneous, runtime-adaptive data processing system, we present an overview of our research into flexible and scalable FPGA accelerators in the form of our template for creating reconfigurable FPGA overlay architectures.

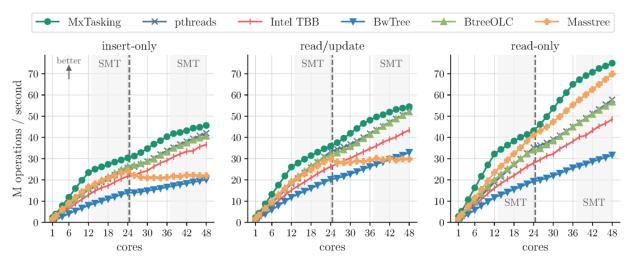

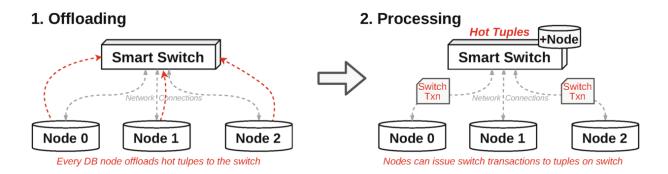

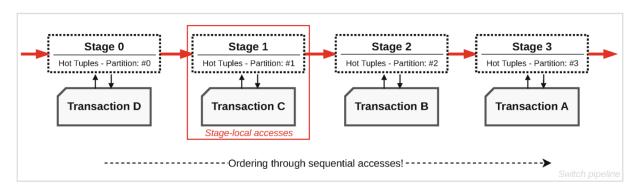

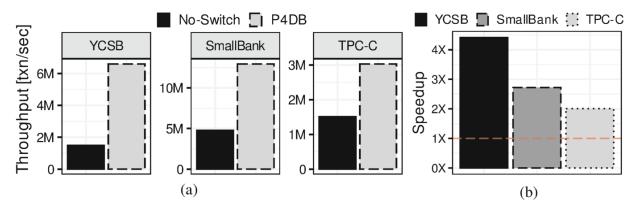

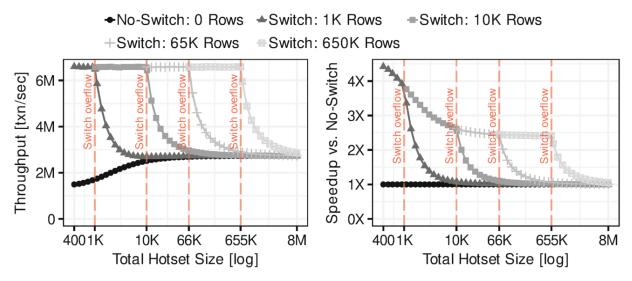

#### 1.5.1 Motivation